2025上半年嵌入式系统设计师第二期模考试卷(应用技术)

摘要:希赛网5月10日-11日举行了2025上半年嵌入式系统设计师第二期模考活动,现将2025上半年嵌入式系统设计师第二期模考试卷(应用技术)分享给大家。有需要的同学可以在本文资料处下载模考试卷的PDF版本。

希赛网2025上半年嵌入式系统设计师第二期模考活动已结束,现将2025上半年嵌入式系统设计师第二期模考试卷(应用技术)分享给大家。模考试卷PDF版本可在本文文首本文资料处或文末的资料下载栏目下载。

2025上半年嵌入式系统设计师第二期模考试卷(应用技术)部分试题如下:

1、

阅读下列说明和图,回答问题1至问题4,将解答填入对应栏内。

【说明】

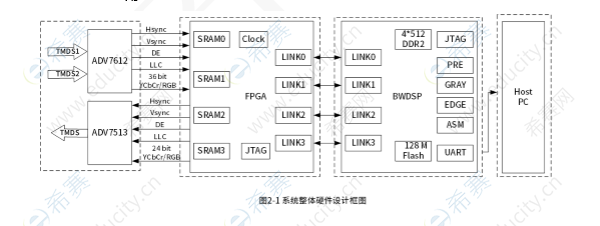

在某嵌入式系统中,视频处理单元负责对接收到的外部视频进行处理和控制。输入包括2路HDMI视频,在视频处理单元中通过叠加、选择、变换等方法输出1路HDMI视频。系统整体硬件设计框图如图2-1所示,包括一个FPGA和一个 DSP处理器,FPGA采用Xilinx公司的 Virtex-5,DSP选用国产BWDSP100处理器,HDMI 视频采集芯片采用ADI公司的ADV7612,HDMI显示芯片选用ADI公司的ADV7513。系统处理器内核1.2V电源采用DC-DC稳压器LTM4616EV,其他电源(2.5V,1.8V,3.3V等)采用德州仪器公司的TPS754xx。外部内存选用镁光公司的MT47H32M16HR-25EIT,NandFlash选用S29GL128N10TA102。

问题内容:

【问题1】(4分)

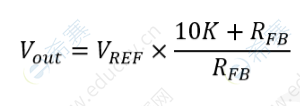

(1)在电源设计中,依据LTM4616EV手册描述,该芯片在5V供电情况下,输出电压可以在0.6V~5V之间任意调节,该系统设计中 FPGA和 DSP 的内核电压均由该芯片提供。在输入电压5V的情况下输出电压的计算公式为

其中,VREF=0.596,RFB为芯片外部的调节电阻,若期望Vout输出1.2V,外部调节电阻RFB应选用如下哪个阻值?

A.5.1k Ω

B.10k Ω

C.6.65kΩ

D.4.87k Ω

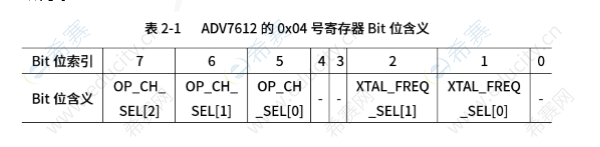

(2)根据HDMI视频采集芯片手册描述,ADV7612可支持四种频率晶振输入,分别是27.000MHz、28.63636MHz、24.576MHz、24.000MHz。在具体使用时需要根据设计来配置ADV7612的0x04号寄存器。ADV7612的0x04号寄存器各个Bit位的含义如表2-1所示。

OP_CH_SEL[2-0]三位用来配置HDMI视频输入线P35-PO(由高到低)各个位含义,对应如下:

000:P35-P24为Y/G,P23-P12为U/CrCb/B,P11-P0为V/R

001:P35-P24为Y/G,P23-P12为V/R,P11-P0为U/CrCb/B

010:P35-P24为U/CrCb/B,P23-P12为Y/G,P11-P0为V/R

011:P35-P24为VR,P23-P12为Y/G,P11-P0为U/CrCb/B

100:P35-P24为U/CrCb/B,P23-P12为V/R,P11-P0为Y/G

101:P35-P24为V/R,P23-P12为U/CrCb/B,P11-P0为Y/G

110:预留

111:预留

XTAL FREQ_SEL[ 1-0]两位用来设置晶振频率,对应如下:

00:27.000MHz

01:28.63636MHz

10:24.567MHz

11:24.000MHz

若该系统的HDMI视频输入线P35-PO配置为U/CrCb/B、Y/G、V/R,晶振频率选择为28.63636MHz,需要将ADV7612的0x04号寄存器配置为多少?(0x04号寄存器的 Bit 0、Bit 3和 Bit 4设置为0)

【问题2】(2分)

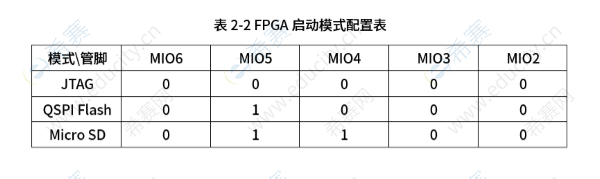

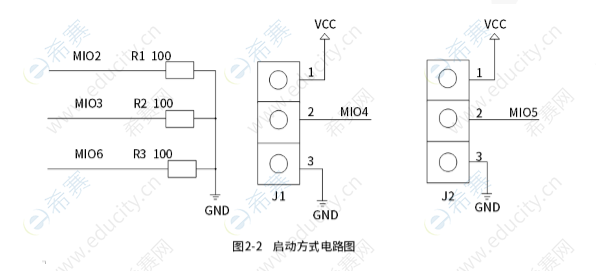

在该系统中,FPGA支持三种启动方式,分别是JTAG、QSPI Flash和 Micro SD,需要利用FPGA的五个管脚MIO[6:2]来配置,对应的配置模式如表2-2所示。

李工设计的启动方式电路图如图2-2所示。

请问:若选用QSPI Flash启动,J1跳线帽应该连接哪两个管脚?J2跳线帽应该连接哪两个管脚?

【问题3】(3分)

李工在实际设计中,需要将FPGA采集到的2路HDMI视频通过专用Link链路传接到BWDSP处理器。2路HDMI输入视频均为1080p,即视频采集分辨率为1920×1080,60帧(每路30帧),每个像素点数据大小为24位,整个Link链路最大可传输带宽为5Gbps。

(1)请问实时传输2路1080p视频数据的带宽要求是多大?

(2)目前设计中的Link链路带宽是否能满足2路1080p视频的实时传输要求?(“Gbps”指速度时,1Gbps = 1000Mbps,1Mbps=1000Kbps,1Kbps=1000bps)

【问题4】(6分)

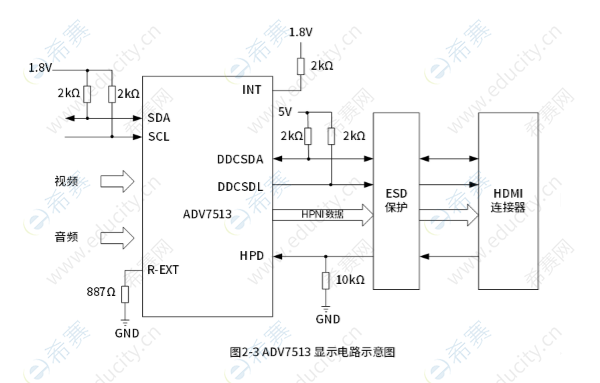

李工设计的ADV7513显示电路示意图如图2-3所示。

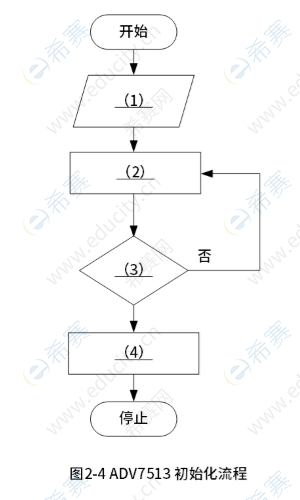

ADV7513的初始化过程描述如下:

FPGA对ADV7513的时钟等先进行初始化,当ADV7513未连接HDMI接收设备时,ADV7513切换为掉电状态,此时ADV7513只有IIC模块和中断检测模块处于工作状态,FPGA通过读取地址为0x42的寄存器来获取ADV7513的HPD检测状态(HDMI外接设备)。当连接HDMI外接设备时,HPD引脚被拉高,触发ADV7513的HPD中断,ADV7513会被唤醒。ADV7513被唤醒后,FPGA需要向ADV7513的断电寄存器0x41的上电标志位写入0,以此启动ADV7513的全部功能。

按照此初始化过程,李工设计了如图2-4所示的ADV7513初始化流程。请根据处理逻辑,从以下选项A~I中选择正确答案,填写空(1)~(4)。

初始化过程的选项:

A.检查ADV7513的HPD位是否有外接设备

B.ADV7513的IIC模块操作

C.ADV7513时钟初始化

D.读取ADV7513寄存器

E.读取ADV7513的0x42寄存器

F.拉高HPD

G.唤醒ADV7513

H.给ADV7513的0x41寄存器上电标志位写1

I.给ADV7513的0x41寄存器上电标志位写0

试题答案:

【问题1】

(1)B (2)0x42

【问题2】

J1跳线帽:管脚2和3

J2跳线帽:管脚1和2

【问题3】

(1)1920×1080×60×24=2.986Gbps

(2)可以满足

【问题4】

(1)C (2)E (3)A (4)I

软考科目怎么选?

微信扫码下方二维码找答案

▼ ▼ ▼

热门:系统集成项目管理工程师备考 | 网络工程师备考 | 软件设计师备考

推荐:信息系统项目管理师网络课堂 | 2026年软考报名时间及入口汇总表

课程:信息系统项目管理师报考指南 | PMP课程

延伸阅读

软考备考资料免费领取

去领取

- 0

- 5

- 1

专注在线职业教育25年

专注在线职业教育25年

扫描二维码

扫描二维码

扫描二维码

扫描二维码